8 Bit Serial To Parallel Converter Verilog Code

Sep 28, 2004 - Keep your verilog FSMs clean. Chertezhi tankov dlya modelirovaniya iz dereva. “Parallel-to-serial converter”. Parallel inputs. Parallel outputs. Serial transmission. Shift Register Application. Binary counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, 001, gray code counter: 000, 010. Four-bit Binary Synchronous Up-Counter.

I am making a parallel to serial converter using ring counter in verilog. The ring counter is working fine but the Parallel to serial converter is not working properly and I am getting x undefined result.

I am providing the code kindly help me finding the problem. TOP module PtoSTOP; reg clk,rst; wire [3:0] myout; wire out; Ring a(clk,rst,myout); parToser x(myout,clk,rst,out); initial begin clk=1; rst=1; #1 rst=0; end always #2 clk=~clk; endmodule Parallel TO Serial Converter module parToser(myout,clk,rst,out); input clk,rst; input [3:0] myout; output reg out; reg [2:0]i; always @(posedge clk or posedge rst) begin if(rst) begin out. I think the main issue you are seeing is part of parToser. You have reg [2:0]i; which you increment and use to address input [3:0] myout; but i can hold values 0 to 7, half of which is outside the address range of [3:0] myout.

You should be seeing a simulation error about out of range addressing. Also you have included a few flip-flops with a reset condition but not added the reset to the sensitivity list in 'parToser' & 'Ring': always @(posedge clk) Should be: always @(posedge clk or posedge rst) With out this trigger your out, i and myout variables will be x, as they have not been set to a known condition. NB: parToser i = i+1; should be i.

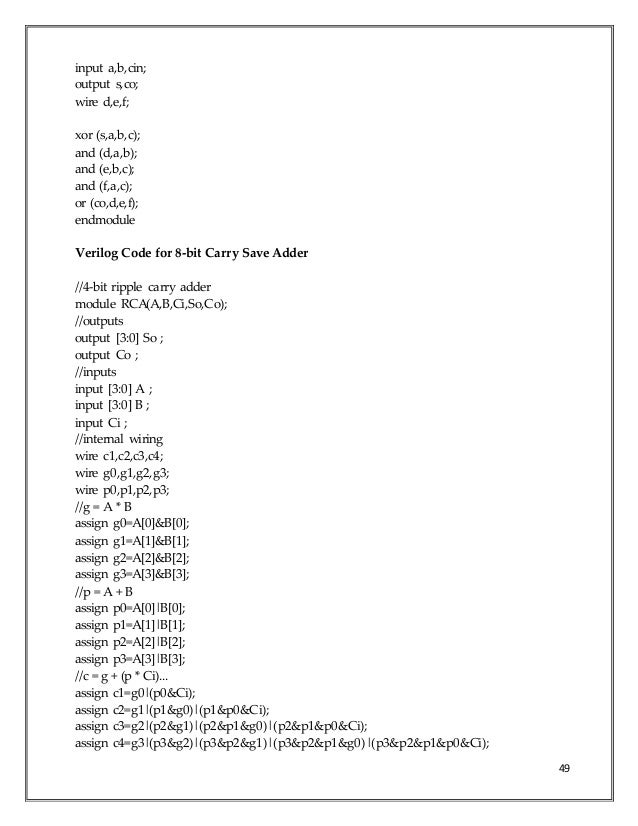

Code Verilog - [ expand] 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 module trai1enc ( din,clk,reset,dout ); output [ 2: 0 ] dout; wire [ 2: 0 ] dout; input [ 3: 0 ] din; input clk; wire clk; input reset; wire reset; reg [ 2: 0 ]s; initial s = 0; assign din [ 0 ] = 1; assign din [ 1 ] = 0; assign din [ 2 ] = 0; assign din [ 3 ] = 1; genvar i; for (i = 0;i.

- четверг 07 марта

- 60